- 您现在的位置:买卖IC网 > Sheet目录1994 > DS3911T+ (Maxim Integrated Products)IC DAC 10BIT I2C QUAD 14TDFN

DS3911

Temperature-Controlled, Nonvolatile,

I2C Quad DAC

17

Maxim Integrated

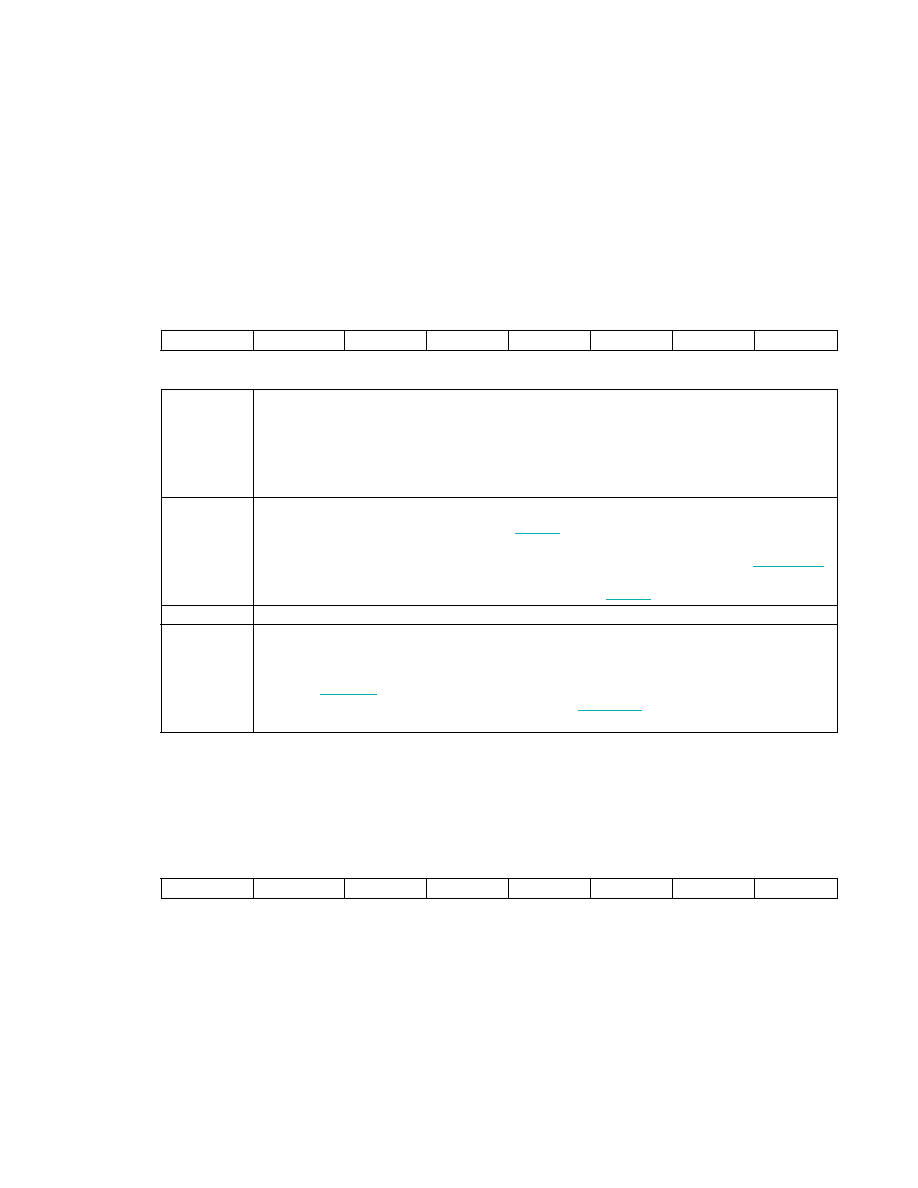

Lower Memory, Register 01h: MODE

Lower Memory, Register 02h: SRAM

POWER-ON VALUE

00h

ACCESS

R/W

MEMORY TYPE

Volatile

02h

SRAM

BIT 7

BIT 0

These general-purpose SRAM bits have no affect on device operation.

POWER-ON VALUE

40h

ACCESS

R/W

MEMORY TYPE

Volatile

01h

SEE

AEN

SRAM

SOFTTXD

BIT 7

BIT 0

BIT 7

SEE: Shadowed EEPROM Disable

0 = Enables EEPROM writes to the shadowed EEPROM bytes.

1 = Disables EEPROM writes to shadowed EPPROM bytes during configuration, so that the

configuration of the device is not delayed by the EEPROM cycle time. Once the values are known,

write this bit to a 0 and write the shadowed EEPROM locations again for data to be written to the

EEPROM.

BIT 6

AEN: Automatic Enable

0 = The temperature-calculated index value TINDEX is writable by the user and the automatic

updates of calculated indexes are disabled. This allows users to interactively test their modules by

controlling the indexing for the LUTs. The recalled values from the LUTs appear in the DAC VALUE

registers after the next completion of a temperature conversion.

1 = The internal temperature sensor determines the value of TINDEX.

BITS 5:1

SRAM: General-Purpose SRAM. These bits have no affect on device operation.

BIT 0

SOFTTXD: Soft Transmit Disable

0 = DACs operate normally.

1 = The DAC outputs are forced to the bit value of the POL bit, which is located in the DAC’s

associate DAC POR register.

For example, when SOFTTXD is set and POL = 1 in the DAC0 POR register, DAC0 is forced to full-

scale output, but if POL = 0, DAC0 is forced to a zero output. This applies to all four DACs.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DS4000KI/WBGA

IC OSC TCXO 19.44MHZ 24-BGA

DS4026S+WCN

IC OSC TCXO 25MHZ 16-SOIC

DS4100HW+

IC OSC CLOCK 100MHZ 10LCCC

DS4266P+

IC OSC CLOCK 266MHZ 10-LCCC

DS4302Z-020/T&R

IC DAC 5-BIT SGL 0-2.0V 8-SOIC

DS4302Z-020+

IC DAC 5-BIT SGL 0-2.0V 8-SOIC

DS4311P+

IC OSC CLOCK 311.04MHZ 10-LCCC

DS4404N+

IC DAC 4CH I2C ADJ 14-TDFN

相关代理商/技术参数

DS3911T+T

功能描述:ADC / DAC多通道 Fast APD Bias RoHS:否 制造商:Texas Instruments 转换速率: 分辨率:8 bit 接口类型:SPI 电压参考: 电源电压-最大:3.6 V 电源电压-最小:2 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-40

DS3920

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Fast Current Mirror

DS3920_1112

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Fast Current Mirror

DS3920T-001+

功能描述:电流和电力监控器、调节器 Fast APD Bias

RoHS:否 制造商:STMicroelectronics 产品:Current Regulators 电源电压-最大:48 V 电源电压-最小:5.5 V 工作温度范围:- 40 C to + 150 C 安装风格:SMD/SMT 封装 / 箱体:HPSO-8 封装:Reel

DS3920T-001+T

功能描述:电流和电力监控器、调节器 Fast APD Bias w/20mA limit

RoHS:否 制造商:STMicroelectronics 产品:Current Regulators 电源电压-最大:48 V 电源电压-最小:5.5 V 工作温度范围:- 40 C to + 150 C 安装风格:SMD/SMT 封装 / 箱体:HPSO-8 封装:Reel

DS3920T-002+

功能描述:电流和电力监控器、调节器 Fast Current Mirror

RoHS:否 制造商:STMicroelectronics 产品:Current Regulators 电源电压-最大:48 V 电源电压-最小:5.5 V 工作温度范围:- 40 C to + 150 C 安装风格:SMD/SMT 封装 / 箱体:HPSO-8 封装:Reel

DS3920T-002+T

功能描述:电流和电力监控器、调节器 Fast APD Bias w/20mA limit

RoHS:否 制造商:STMicroelectronics 产品:Current Regulators 电源电压-最大:48 V 电源电压-最小:5.5 V 工作温度范围:- 40 C to + 150 C 安装风格:SMD/SMT 封装 / 箱体:HPSO-8 封装:Reel

DS3922T+

制造商:Maxim Integrated Products 功能描述:ADV APD MIRROR W/INT FET & STAT OUT - Rail/Tube 制造商:Maxim Integrated Products 功能描述:IC CURRENT MIRROR TQFN